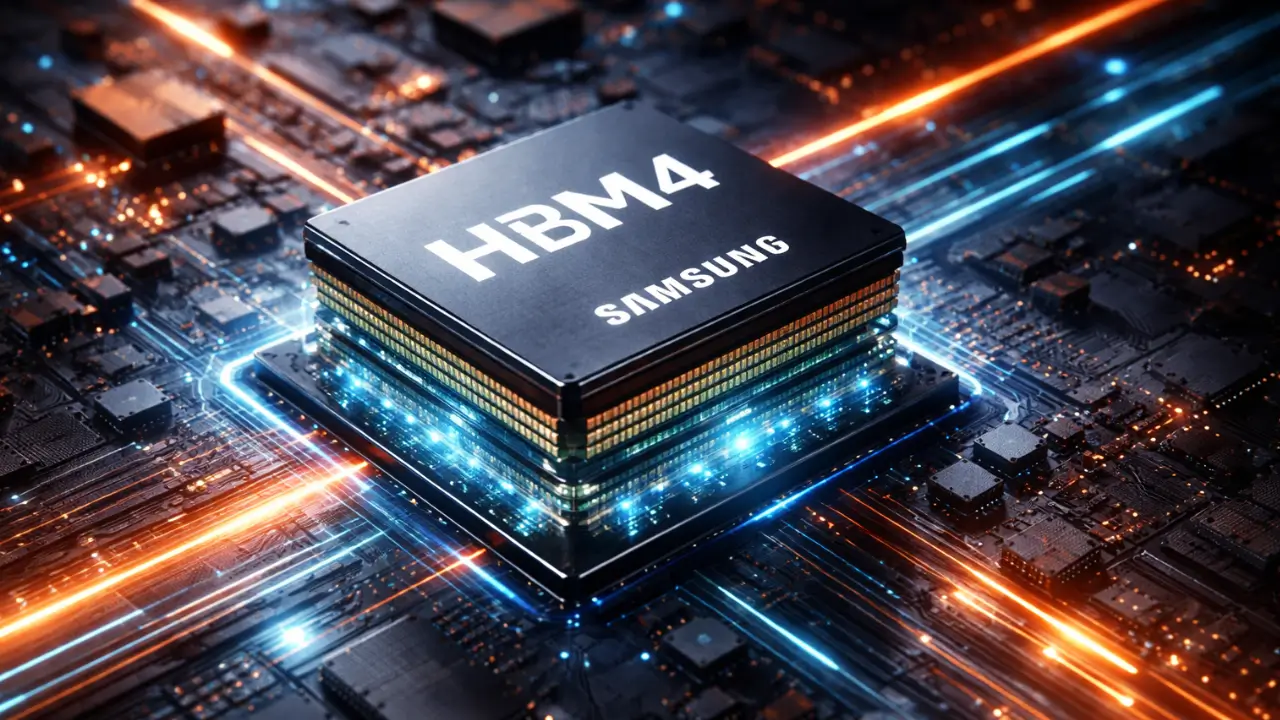

The AI infrastructure race has reached a new inflection point. Memory not compute now defines the ceiling of artificial intelligence performance. Samsung Electronics has moved that ceiling upward.

The company has begun mass production of HBM4 and shipped commercial products to customers, positioning itself at the forefront of the next-generation high-bandwidth memory market. The move signals more than a product milestone; it marks a structural shift in how AI systems will scale over the next decade.

Unlike incremental upgrades, HBM4 arrives as a strategic lever. It compresses latency, expands bandwidth, and reshapes the cost-performance curve of GPUs, accelerators, and hyperscale AI clusters.

Samsung Bets on Advanced Nodes to Leapfrog the Market

Samsung built its HBM4 on its sixth-generation 10nm-class DRAM process (1c), alongside 4nm logic technology. Instead of relying on proven designs, the company pushed directly into advanced nodes, accelerating performance gains while stabilizing yields at scale.

“Instead of taking the conventional path of utilizing existing proven designs, Samsung took the leap and adopted the most advanced nodes like the 1c DRAM and 4nm logic process for HBM4,” said Sang Joon Hwang, Executive Vice President and Head of Memory Development at Samsung Electronics. “By leveraging our process competitiveness and design optimization, we are able to secure substantial performance headroom, enabling us to satisfy our customers’ escalating demands for higher performance, when they need them.” This approach reflects a broader strategic logic: in AI infrastructure, memory leadership increasingly determines platform dominance.

HBM4 Performance: Redefining AI Throughput

Samsung’s HBM4 delivers a processing speed of 11.7Gbps, surpassing the industry baseline of 8Gbps by roughly 46%. Compared with HBM3E, the new memory generation improves peak pin speed by 1.22x, while scaling further toward 13Gbps.

Bandwidth expansion is even more consequential. A single HBM4 stack reaches up to 3.3TB/s 2.7 times higher than HBM3E. For hyperscalers and GPU vendors, this translates directly into higher model throughput and reduced bottlenecks in large-scale AI training and inference.

Capacity scaling follows a similar trajectory. Samsung offers 24GB to 36GB configurations using 12-layer stacking, while 16-layer stacks will extend capacity to 48GB, aligning with future AI workload requirements.

Power Efficiency Becomes the Real Differentiator

As AI architectures expand, energy efficiency increasingly determines economic viability. HBM4 addresses the doubling of data I/O pins from 1,024 to 2,048 through low-power design innovations integrated at the core die level.

Samsung reports a 40% improvement in power efficiency through low-voltage TSV technology and optimized power distribution networks. Thermal performance also improves, with 10% stronger resistance and 30% better heat dissipation than HBM3E. These gains matter beyond benchmarks. They directly influence total cost of ownership, data center density, and the scalability of next-generation AI clusters.

The Roadmap Beyond HBM4

Samsung’s HBM4 strategy extends beyond performance metrics. The company is leveraging its large-scale DRAM manufacturing footprint, integrated foundry-memory optimization, and advanced packaging capabilities to secure production resilience.

Design Technology Co-Optimization between foundry and memory divisions accelerates yield stabilization and reduces lead times. At the same time, Samsung plans to deepen collaboration with GPU manufacturers and hyperscalers focused on next-generation ASIC platforms. This integration reflects a structural reality: AI memory has become a geopolitical and industrial asset, not just a semiconductor product.

Samsung expects its HBM sales to more than triple in 2026 compared with 2025. The company is expanding HBM4 production capacity while preparing the next phase of its roadmap.

HBM4E sampling is expected in the second half of 2026, followed by custom HBM solutions reaching customers in 2027. The timeline signals a sustained acceleration in AI memory innovation, rather than a single generational leap.

Why HBM4 Changes the AI Infrastructure Equation

HBM4 does not simply upgrade memory performance. It changes how AI systems scale. As models grow larger and more compute-intensive, memory bandwidth increasingly determines real-world performance. Samsung’s early commercial shipment of HBM4 suggests that the next wave of AI competition will unfold not only in GPUs and accelerators, but in memory architecture.

In that sense, HBM4 represents more than a technical milestone. It marks the beginning of a new strategic layer in the global AI compute stack, where memory leadership may decide who wins the AI decade.